Första FPGA:an med hårda block för flyttal

Första FPGA:an med hårda block för flyttal

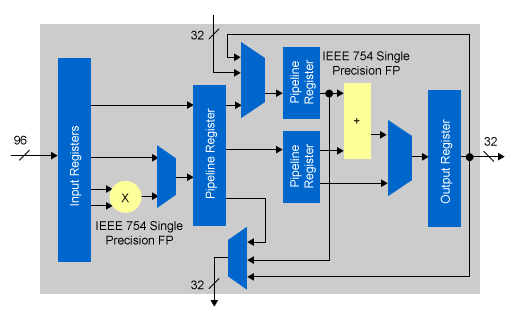

Genom att öppna en funktion i sitt designverktyg kan redan levererade FPGA:er i Arria 10-familjen prestera upp till 1,5 TFLOPS. Beräkningskraften i de hårda flyttals-DSP:erna går att nå via OpenCL, DSP Builder eller traditionell HDL-kod.Altera blir först ut med dedicerade block för flyttalsberäkningar. Tilläggas kan att det handlar om enkel precision enligt IEEE 754.

Borrar man lite djupare visar det sig att flyttalsblocken utnyttjar delar av de existerande blocken för heltal. På så sätt kan Altera skicka med flyttalsfunktionen i alla Arriakretsar på 20 nm utan att det kostar något extra.

För övrigt kommer samma DSP-block att finnas i den kommande Stratix 10-familjen som ska tillverkas av Intel på 14 nm. När produktionen startar någon gång nästa år lyfter prestanda från 1,5 TFLOPS med Arria till 10 TFLOPS. Dessutom ska det gå att flytta en konstruktion från Arria till valda delar av Stratix-familjen utan problem, lovar Altera.

Även om flyttalsfunktionen finns i redan levererade kretsar, och det går att designa för dem, dröjer det till hösten innan man kan ladda ned koden till FPGA:erna och köra skarpt. Under tiden får användarna nöja sig med en mjuk implementation i logikdelen för att testa flyttalsfunktionen.