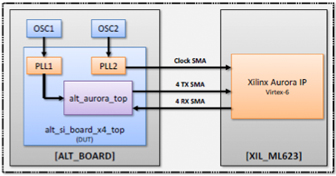

Normalt brukar man behöva välja antingen Altera eller Xilinx när man ska utveckla ett FPGA-baserat system. Franska Reflex ställer den här regeln på huvudet med ett IP-block som gör det möjligt för en Virtex att kommunicera direkt med en Stratix via Aurora-protokollet.

– Den här IP-kärnan gör att du kan blanda kort med FPGA-kretsar från Altera och Xilinx i samma system och använda ett enda höghastighetsprotokoll för att kommunicera mellan kretsarna, förklarar Sylvain Neveu på Reflex.Aurora är ett öppet och skalbart protokoll från Xilinx för länklagret. Det används för att flytta data över seriella länkar och kan används av högre lagers protokoll för kommunikation till kretsen.

– Vi har många förfrågningar från europeiska, amerikanska och asiatiska kunder med industriella och militära tillämpningar som vill använda stora Alterakretsar samtidigt som de är kompatibla med Virtexfamiljen från Xilinx, säger Sylvain Neveu.

Till att börja med stöds kommunikation med full duplex mellan Virtex-6 LXT och Alteras Stratix IV och Stratix V GX. Det går att skapa upp till 16 kanaler med 3,125 Gbit/s vardera.

IP-blocket som placeras i FPGA:an från Altera upptar mindre än 900 ekvivalenta logikceller för en kanal. För fyra kanaler behövs lite mer än det dubbla, det vill säga 2000 logikceller.